|

|

近年半導体の微細化技術が限界近くなり、小型化や更なる高機能化研究開発にハイブリッドチップの期待も強く積層型(スタック/3D)半導体(SOC IC)による半導体の進化が注目されています。

この半導体チップ高精度アライメントスタッキング装置「HPAS Mono」はスタック手法を用いたヘテロ構造の半導体開発用途にカラー画像解析及び高精度の位置合わせをソフトウエアコントロールで高速に行う事が可能です。

Z方向のスタッキングステップあたり50 nmの優れた信頼性の高いスタッキング調整可能です。

高精度の位置合わせタスクは、外部からソフトウェア制御で実行されます。

又、コンパクトな装置ですのでグローブボックスでの操作可能で酸化や汚染を最小限に抑えます。

カスタマイズのフランジキットを使用して不活性ガスチャンバーを使用することもできます。

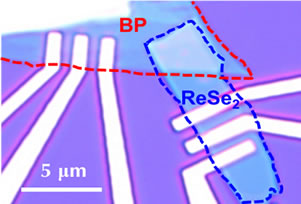

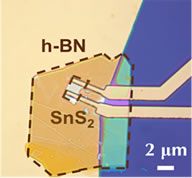

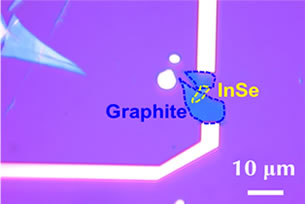

【ヘテロ接合デバイス】 |

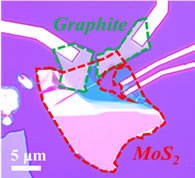

【Homojunctionデバイス】 |

【ヘテロ接合デバイス】 |

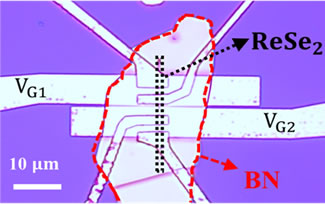

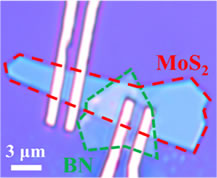

【2Dコンタクトデバイス】 |

【2D基板デバイス】 |

| MAIN FEATURES | |

|---|---|

| マシンステージ | ソフトウエア |

| ・XYZ resolution ≈ 50 nm/step ・Rotation resolution ≈ 0.056° ・移動範囲(XYZ)≈2 x 2 x 5 cm ・コンピュータ制御ステージコントロール |

・ライブビュー操作 ・コンピュータ支援フォーカス ・コントラスト強化 ・Object tracking ・Image overlapping ・RGB厚さ分析 |

| Microscope | |

| 耐物レンズ | カメラ |

| ・倍率= 20 X ・Numeric aperture(開口数)= 0.45 ・アシストイルミネーション |

・高感度センサー ・静的解像度:6 MP ・HDビデオ:1080p |

| DIMENSIONS | |

| Main Body | PC必要条件 |

| ・Dimension (mm): 450 x 300 x 500 (H) ・Weight (kg): 18 ・Power: DC 12V 10A (In: 100-240V AC @ 50/60Hz) ・Sample Working Space (mm): 20 x 20 x 50 (H) ・Sample Size (mm): < 20 x 20 |

・Windows 64bit, 8 or 10 ・CPU: Intel i5 quad-core with 8GB RAM ・USB: 2 Ports |

★ 上述数値・仕様は製品改良等により予告なしに変更される場合があります。

【スタッキング方法・手順】

Preparation

1. 機械的な剥離又はCVD成長による原子レイヤーをターゲット基板に転写します。

2. 他の原子レイヤーをポリジメチルシロキサン(PDMS)等透明なスタンプに転写します。

Stacking

上述用意した2つの材料をそれぞれモーターステージとサンプルホルダーに配置します。

本装置ソフトウエアAligning & Stacking toolsを使用して位置合わせを開始します。

ソフトウエアインターフェースにより正確に(50 nm ステップ, 0.056°)位置決めし2つを結合し完了確認後開放してスタッキング完了します。

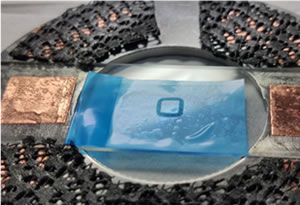

【PDMS Transfer】 |

【Focus and Position】 |

【Align and stack】 |

【Inspection】 |

【ソフトウエアAligning & Stacking tools】

XYZ軸 各50nmステップ、角度分解能0.056°を持ち電動ステージコントロールで正確に位置決め可能。

「マジックアングル」グラフェン(magic angle graphene)や「異方性の材料 (Anisotropic Materials)」の研究にも活用・応用可能です。

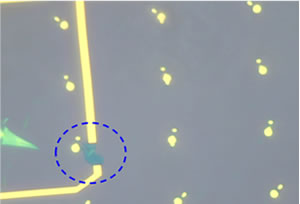

【Object Tracking】 ライブビューモードでエッジを検出し、高速で正確な位置合わせを可能にします。 例:PMDSサンプル |

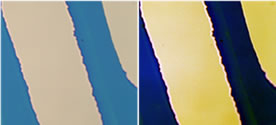

【コントラスト機能】

ライブビューモードでの色のコントラストを改善します。 |

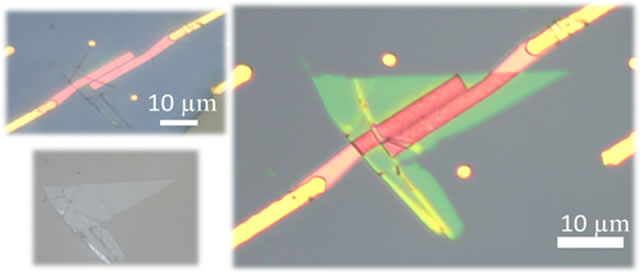

【Image Overlapping】 異なる深度でキャプチャされた画像を比較する事で簡単に異なる深度の対象物を位置決め出来ます。 |

【RGB分析】 4つのチャネル(赤/緑/青/灰色)のRGBコントラストデータベースより材料の厚さを導き出し、2D材料の複数レイヤを最大限識別します。 (使用する顕微鏡とカメラモジュールに依存。) |

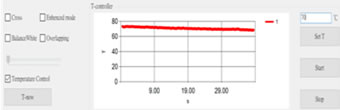

【温度コントロール】 リアルタイムのPIDソフトウェア制御により室温から150℃までの加熱が可能です。 |